CACHE COHERENCE VS CONSISTENCY UPDATE

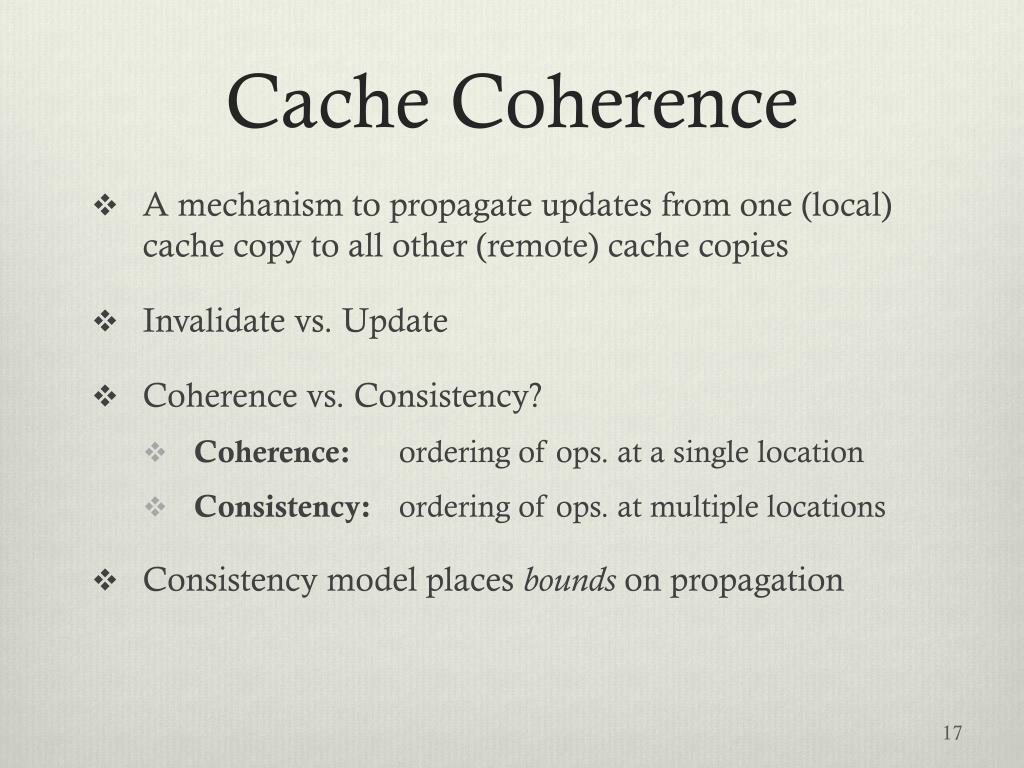

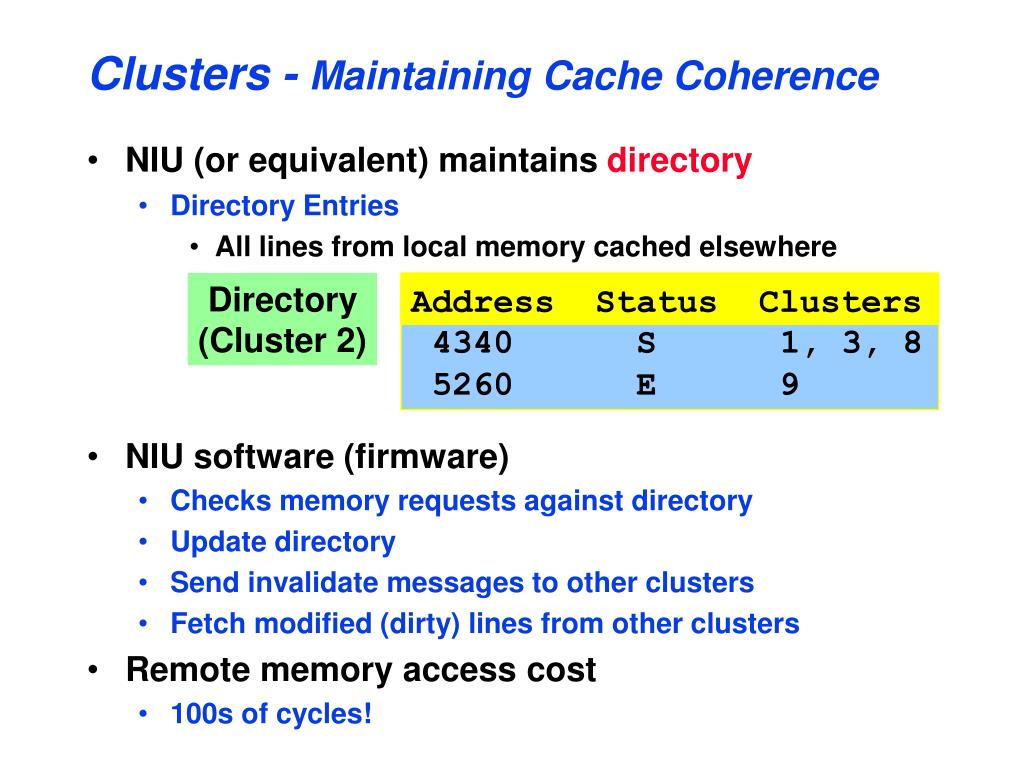

This second edition reflects a decade of advancements since the first edition and includes, among other more modest changes, two new chapters: one on consistency and coherence for non-CPU accelerators (with a focus on GPUs) and one that points to formal work and tools on consistency and coherence. Cache Coherence Solution Bus-Snooping Protocols: (Not scalable) Used in bus-based systems where all the processors observe memory transactions and take proper action to invalidate or update the local cache content if needed. We present both high-level concepts as well as specific, concrete examples from real-world systems. This understanding includes both the issues that must be solved as well as a variety of solutions. The goal of this primer is to provide readers with a basic understanding of consistency and coherence. As part of supporting a memory consistency model, many machines also provide cache coherence protocols that ensure that multiple cached copies of data are kept up-to-date. Consistency definitions provide rules about loads and stores (or memory reads and writes) and how they act upon memory. For a shared memory machine, the memory consistency model defines the architecturally visible behavior of its memory system. In a shared memory system, each of the processor cores may read and write to a single shared address space. Compile-time classification identifies most accesses as private, enabling significant optimizations in the cache coherence protocol.Ī Dual-Consistency Cache Coherence Protocol Ros A., Jimborean A.Many modern computer systems, including homogeneous and heterogeneous architectures, support shared memory in hardware. memory page) and temporality (i.e., the classification is valid during the execution of the region vs. Therefore, SPEL considers both a finer granularity (size of accessed data vs. In contrast, the compiler performs a classification by regions, where a memory access is private (or shared but read-only) if the target address is accessed by a single thread within the region. Hence, in practice, the majority of memory accesses are eventually classified as shared.

Operating-system (OS-based) classification: The operating system classifies a memory access as private if the corresponding memory page is referenced by a single thread during the entire execution. Compared to a standard directory protocol, we show improvements in performance of 24% and reductions in energy consumption of 32%, on average, for a 64-core chip multiprocessor.Ĭlassification of memory accesses as private or shared: Compile-time (xDRF) vs.

CACHE COHERENCE VS CONSISTENCY CODE

Outside these regions, code is executed under a more restrictive protocol which enforces sequential consistency.

This audience includes computing industry professionals as well as junior graduate students. The design of the protocol exploits a compile-time identification of code regions which can be executed under a less restrictive, thus optimized protocol, without harming correctness. This primer is intended for readers who have encountered cache coherence and memory consistency informally, but now want to understand what they entail in more detail. This work proposes SPEL, a dual-consistency cache coherence protocol which simultaneously guarantees the strongest memory consistency model provided by the hardware and yields improvements in both performance and energy consumption. The design of an efficient system with an intuitive memory model is an open challenge.

Weak memory consistency models can maximize system performance by enabling hardware and compiler optimizations, but increase programming complexity since they do not match programmers' intuition.

Uppsala Architecture Research Team A Dual-Consistency Cache Coherence Protocol

0 kommentar(er)

0 kommentar(er)